#### **PAPER • OPEN ACCESS**

## An Efficient Interconnection System for Neural NOC Using Fault Tolerant Routing Method

To cite this article: A. Pradeep kumar et al 2021 J. Phys.: Conf. Ser. 2089 012069

View the article online for updates and enhancements.

### You may also like

- Design and testing of high-speed interconnects for superconducting multi-<u>chip modules</u> S Narayana, V K Semenov, Y A Polyakov

- et al.

- DI GA: A Heuristic Mapping Algorithm for Heterogeneous Network-on-Chip Juan Fang, Huan Zong and Haoyan Zhao

- Three-dimensional culture of epidermal cells on ordered cellulose scaffolds Tomoko Seyama, Eun Young Suh and Tetsuo Kondo

2089 (2021) 012069

doi:10.1088/1742-6596/2089/1/012069

Journal of Physics: Conference Series

# **An Efficient Interconnection System for Neural NOC Using Fault Tolerant Routing Method**

#### Dr.A.Pradeep kumar<sup>1</sup>, Y. Devendar Reddy<sup>2</sup>, Dr.T.Srinivas Reddy<sup>3</sup>, K. Jamal<sup>4</sup>

<sup>1</sup>Professor, Mallareddy Engineering College (A), Hyderabad, Telangana, India

Email: pradeepkumar@mrec.ac.in

Abstract. Large scale Neural Network (NN) accelerators typically have multiple processing nodes that can be implemented as a multi-core chip, and can be organized on a network of chips (noise) corresponding to neurons with heavy traffic. Portions of several NoC-based NN chip-to-chip interconnect networks are linked to further enhance overall nerve amplification capacity. Large volumes of multicast on-chip or cross-chip can further complicate the construction of a cross-link network and create a NN barrier of device capacity and resources. In this paper, this refer to inter-chip and inter-chip communication strategies known as neuron connection for NN accelerators. Interconnect for powerful fault-tolerant routing system neural NoC is implemented in this paper. This recommends crossbar arbitration placement, virtual interrupts, and path-based parallelization strategies in terms of intra-chip communications for the virtual channel routing resulting in higher NoC output at lower hardware costs. A lightweight NoC compatible chip-to-chip interconnection scheme is proposed regarding to inter-chip communication for multicast-based data traffic to enable efficient interconnection for NoC-based NN chips. Moreover, the proposed methods will be tested with four Field Programmable Gate Arrays (FPGAs) on four hard-wired deep neural network (DNN) chips. From the experimental results it can be illustrate that a high throguput can obtained effectively by the proposed interconnection network in handling thedata traffic and low DNN through advanced links.

**Keywords:** Network-On-chip (NoC), Deep Neural Network (DNN), Interconnection Architecture, Chipto-chip interconnection, Hardware Accelerator,

#### 1. Introduction

Technology can combine more and more logic circuits into a single chip. Therefore, the chips characters became more powerful. Processing units are integrated within a sigle chip which work with different clock frequencies [1] [2]. Traditionally, processing units have to interconnect the various sections of the SoC using bus structures. However, bus system on chip (SoC)s are key connectivity schemes because their scalability is too low [1]. Network on a chip has been suggested as a possible candidate for reduced scalability and poor connectivity efficiency issues presented in the previous SoC. Network connectivity is used by the NoC as a subtitut of bus systems to provide Globally Asynchronous and Locally Synchronous data transfer (GALS); that ensures that NoCs have increased the reliability of network connectivity and power usage by on-chip logic and device complexity [2].

The continuous increase in the size and complexity of the NoC interconnect infrastructure presents major challenges to the time-tested initiative of the architecture [3]. Chips up to 100 cores today rely on a wide range of NoC connectivity. In addition, active interconnecting architectures are being implemented to provide better efficiency and power utilization. This increasing maturity is obvious when one explores the growing concerts of features integrated into the router architecture, including complex arbitration processes, speculation as well as adaptive routing [4].

<sup>&</sup>lt;sup>2</sup>Associate Professor, Nalla Narasimha Reddy Education Society's Group of Institutions, Hyderabad, Telangana, India

<sup>&</sup>lt;sup>3</sup>Professor, Mallareddy Engineering College (A), Hyderabad, Telangana, India

<sup>&</sup>lt;sup>4</sup>Assistant Professor, GRIET(A), Hyderabad, Telangana, India

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

**2089** (2021) 012069 doi:10.1088/1742-6596/2089/1/012069

In addition adopting of dynamic overlay communication protocols, advanced routing protocols and custom power & plug devices is the added difficulty. This complexity of design highly represents a large area of design which may not fully implemented and verified in the design review phase. Interconnect designs therefore can be sold in some unconfirmed versions with hidden defects in the corners. NoC is same as that of traditional embedded network utilized in parallel multiprocessor computers but the NoCs have unique characteristics contrasting to the parallel computers. The important variations between NoC and parallel computers are energy use restricted design specialization and the area and variety of materials used. The power consumption is the main limitation of the NoCs in most of the battery-operated NoCs applications. Therefore the main objective of the NoC structure is to maintain a device with low power consumption.

In addition, NoC can be designed for separate and separate applications from parallel computer network for a variety of unknown applications. In addition to memory and processors, a variety of modules can be assigned to a single nose and include Digital Signal Processing (DSP) and FPGA architecture, making noise more extensible. Applications implemented in NoC designs usually have limited configuration tools and strict performance characteristics. The way in which application performance meets benchmarks with minimal capital is the main confront of NoC architecture. Capital constraints require more appropriate algorithms and more expensive NOCs [5].

As a result, the critical routing algorithm is now the primary routing algorithm for NoCs. With the level of NoC increasing, the growing debate over data transfer calls for expansion of the cache capacity of routers will increase. As a result, artificial channel models are installed in the router. The seperate memory is configured by partitioning the physical memory in which multiple data packets are stored that reduces the router buffer load on chip. The way of reducing friction is the significant method to improve efficiency of router.

The buffer size on the NoC router needs to be reduced, which can be solved using virtual channels. The main challenge of the NoC architecture is how to meet application performance standards using minimal capital. Capital constraints require more appropriate algorithms and more expensive NoCs. As a result, the decisive routing algorithm has now become the primary routing algorithm for NoC. With the reduction of NoC, the growing debate about data transfer requires expanding the buffer capacity of routers.

As a result, synthetic channel models are installed in the router. Multiple data packets are stored in a separate memory by setting the physical memory partition to reduce the buffer load of the on-chip router. The rest of the data fits are tracked by the header flip in a pipeline manner. If the header blocks flight, the rest of the flight will also stop on simulation channels. Since packets need to be fixed in a single virtual channel instead of the entire buffer, routers can be configured with some default channel buffers for each terminal. Digital channels can also be used to reach higher channel capacity at lower cost.

#### 2. Related Work

NN's hardware acceleration has attracted tremendous attention in recent years However, DNN-based interconnection networks have very few contributions. New- hub proposes a hybrid ring mesh for neuromorphic systems designed to accelerate the multilayer perception. In new-NoC, single-layer neurons are connected to a ring and single-ring neurons share the same data for multicast traffic. These local circuits are connected to each other through the NoC mesh to influence data movements between different layers. The ring topology is often affected by output and delay. Proposes a closed topology-based indirect interconnection network customized for close NN feed-forward NNs. This overcomes the narrow bending bandwidth of the tree and the large diameter of the mesh topology, which shows the reliability of the power supply in handling multicast traffic. However, the structure suffers from the physical limitations of the cable.

**2089** (2021) 012069 doi:10.1088/1742-6596/2089/1/012069

Eyeriss offers a Hierarchically Overlapping Network (HM-NoC) for DNNs. Processing Elements (PES) and Global Buffer (GLB) are grouped and linked by HM-NoC. NoC can be configured in several circuit-switched routing modes depending on the type of data transmitted. With enhanced NoC, different types of data (input activation, partial weights and volumes), from high bandwidth to high data reuse, can be exchanged between PEs and GLBs. The large tree topology was used for internal and network communication over Hyper Transport 2.0 to monitor data traffic between chips in large-scale NN architectures. However, advanced intra-chip and inter-chip architectures do not fully accept multicast DNN traffic, which can deter network amplification systems.

#### 3. Literature Survey

Hierarchical agent architecture is suggested to provide on-line management capabilities for NoC-based applications. Unit structures are optimally maintained by agents at each construction level based on the circuit conditions monitored during runtime. This paper explores the monitoring relationship between the level of the agent and focuses on the alternatives for system optimization to be handled at various levels of the agent. They recommend the hierarchical configuration of the agent with the appropriate monitoring services. This architecture introduces a level of control into the NoC network hierarchy.

This layer provides the scalability and increased flexibility of large-scale NoC systems designed to maximize device performance by balancing all of the chip resources. Hierarchical approaches is used for multi-capacity management services and fault tolerance management. The hierarchical agent simulation approach is excellent at achieving self-conscious and parallel computing in a scalable manner. A hierarchical agent that controls device status during runtime and re-configures components to boost performance in the event of an error.

The method of manufacturing a complex device, such as a chip network, will trigger several failures. Inexpensive routing algorithms are used in NoC to support permanent fault connections. Use appropriate simulation and synthesis to measure efficiency, power consumption and area overhead to see the effect of these algorithms. Proposed error-tolerant routing algorithms that can be reconstructed which make decisions based on local error information stored at each node and in the current and destination node configuration register which is obtained [6].

The first routing algorithm (FT XY) tolerates a fault link. (FT XY2) & (FT XY3) is an extension (FT XY) to find two other defective links, considering the hardware overhead gap. According to simulation and synthesis, the proposed routing algorithm does not enable VCs to have minimal overhead and overhead capability. The Fault-on-Neighbor (FoN) routing algorithm for NoC is proposed in clause, which sets out the routing decision on the basis of the connection status of the neighboring switches within 2 hops in order to prevent incorrect connections and switches. Diversion routing is a compatible routing algorithm that is essentially implemented to hardware, which ensures that packet buffers are not used while shipping. Fault – on - Neighbor (FoN) conscious variance routing algorithm based on the distribution of incorrect information in 2 zones to prevent defective links and switches and to preserve clear convex and concave error zones without blocking or blocking existence.

Fault-tolerant routing can be divided into two classes: random and critical. It transmits unwanted packets over various channels to stop random communication errors. The critical algorithm is used NoC architectural redundancy to transport packages to the destination through various means to achieve fault tolerance. The decision to route Forced Wormhole Routing (FWR) is based on the buffer state of the routing table and neighboring keys. Use first level packet as visibility to check queue and adjacent key buffer status. This section specifies the NoC fault-tolerant elastic routing algorithm based on the turn model.

**2089** (2021) 012069 doi:10.1088/1742-6596/2089/1/012069

When ensuring proper service, the switch can be rebuilt around broken components without the use of virtual networks. A fault-based positive deflection routing algorithm has been proposed that allows decision-making on cost-function-based routing. The switch implements an online troubleshooting approach and makes a routing decision based on a cost function that takes root duration and local fault status into account. Not only can it handle connecting and turning errors, but it can also handle crossbar errors. Since routing decisions are based solely on inaccurate knowledge of the current transfer, the packet hop count region can be easily overwhelmed by some faulty versions.

The geometry of the NoC is based on Nostrum NoC, a 2D mesh topology. It varies from a typical 2D network in that the limit output is attached to the same switch input and the packet sent in that direction is returned to the same switch. It can be used as a buffer for packets. Distraction routing is used to make a routing decision depending on the priority packet and the next network load voltage varies over the last 4 cycles. The two incoming packets are chosen on the basis of their hop count, which shows the number of hop packets. The packet with the largest number of hops shall have the highest preference. Requires high to low priority routing alternatives for packet relocation.

Device configurations are favorably controlled by agents at each construction level based on circuit conditions tracked at runtime. Device configurations provide periodically configured resource consumption and power supply. This technology provides a comprehensive approach to the design of VLSI (Very Large Scale Integration) circuits under the control of variations and strict power limits.

By implementing a bio-induced agent-based hierarchical modeling approach bio-induced system architecture, the design framework NoC proposed for hierarchical agent monitoring. Bio-induced approach-agent mechanisms have appealing network implementation characteristics such as scalability and compatibility, bio-induced system architecture divides conventional control resources across different agent layers and is more scalable than traditional systems.

They propose a hierarchical control factor based on an engineering approach, shaped by the joint efforts of hierarchical intelligent agents to plan, manage and fine-tune the NoC system at various operational levels, including system outputs, energy efficiency, fault tolerance and diversity. Provides high-level capture of concurrent control functions through distributed networks. Here, each stage of the agents carries out special controls on the basis of their detail. The monitoring process and tasks are distinguished by an unmistakable fixed structure of the system.

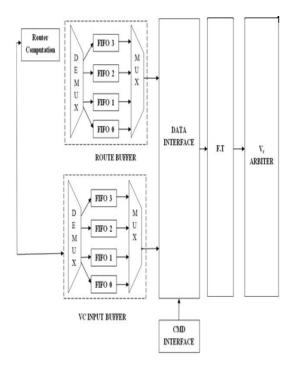

#### 4. Fault Tolerant Routing Interconnect System For Neural NoC

The below figure (1) shows the architecture of fault tolerant routing interconnect system for neural NoC. A new routing strategy is being implemented to address imbalanced data-dependent network loads on multiple virtual networks. It has an eastern port, a western port, a northern port, a southern port and a domestic port. Each terminal has four simulation channels. An escape network can be set up by gently creating one channel for each router. The third default channel for each router is not accessible at the start of the transmission. The data packet is sent to the third virtual channel only when the queue time limit of other channels is reached and the other channels are sent to the destination without access.

The basic Y-X routing strategy is discarded in order to avoid competition at the exit ports. The leak network is used to pass packets from the usual channel to the leak channel only after data packets have been waiting for a long time in the simulation channel. However, data packets using X-Y routing in the normal channel and packets in the loss network must be transmitted simultaneously, since data packets in the normal channel and data packets in the loss channel which vary from the same output channel.

**2089** (2021) 012069 doi:10.1088/1742-6596/2089/1/012069

Fig. 1. Architecture Of Fault Tolerant Routing Interconnect System For Neural NoC

When NoC runs at a lower data injection rate, NoC's delay is greater than that of traditional mesh-based NoC. The condition is changing as the pace of data injection rises. This is because the data packets buffered in the virtual channel do not wait long when NoC has a lower data injection rate. The waiting time, however, does not reach the limit. It provides control and retrieval function for the reception and distribution of data to the entire arbitration system. Statements of VCs (Version Control systems) are mediated according to the credit of the target VC and the preference of the local VC.

In addition, it is responsible for sending and analyzing instructions. The credit synchronization system is used here to prevent overloading the RX handle. This module sends a request for a credit update based on the RX level and receives a credit order from another chip to change the local credit. If the credit is reduced to 0, the goal on the RX side means that the VC is complete.

For convenience, this has just mentioned five types of commands. When an error occurs, the data link layer sends a credit synchronization order only. In most instances, the machine sends good data instead of a command. Compared to PCI's (Personal Computer Interconnects) packet redundancy in the network connection layer, this architecture has fewer overheads and is likely to improve efficiency substantially.

#### 5. Results

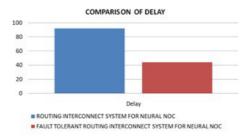

The below figure (2) shows the comparison of delay in fault tolerant routing interconnect system for neural NoC and routing interconnect system for neural NoC. From this figure it can observe that the fault tolerant routing interconnect system for neural NoC reduces the delay very effectively.

**2089** (2021) 012069 doi:10.1088/1742-6596/2089/1/012069

Fig. 2. Delay Comparison

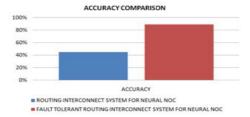

The below figure (3) shows the comparison of accuracy of in fault tolerant routing interconnect system for neural NoC and routing interconnect system for neural NoC. In fault tolerant routing interconnect system for neural NoC accuracy is very high. It gives effective output and reduces the fault very efficiently.

Fig. 3. Accuracy Comparison

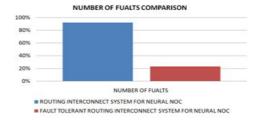

The below figure (4) shows the comparison of reduction of number of faults in fault tolerant routing interconnect system for neural NoC and routing interconnect system for neural NoC. Compared to both number of faults are reduced in fault tolerant routing interconnect system for neural NoC.

Fig. 4. Number of Faults

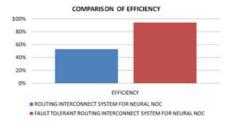

The below figure (5) shows the comparison of efficiency of fault tolerant routing interconnect system for neural NoC and routing interconnect system for neural NoC.

Fig. 5. Efficiency

**2089** (2021) 012069

doi:10.1088/1742-6596/2089/1/012069

#### 6. Conclusion

Hence in this paper, this has suggested an efficient fault-tolerant interconnecting mechanism for neural NoC. Interconnection to handle the tremendous amount of multicast-based traffic in DNN accelerators effectively. The interconnection shall be thoroughly tested using the RTL (Register Transfer Level) time consistency model. It is also interconnected with four hardware systems focused on FPGA (Field Programmed Gate Array). From results it can observe that it occupies less area, reduces the delay and increases the accuracy of system.

#### References

- [1] S. Yin et al., "An energy-efficient reconfigurable processor for binaryand ternary-weight neural networks with flexible data bit width," IEEE J. Solid-State Circuits, vol. 54, no. 4, pp. 1120–1136, Apr. 2019.

- [2] Y.-H. Chen, T.-J. Yang, J. S. Emer, and V. Sze, "Eyeriss v2: A flexible accelerator for emerging deep neural networks on mobile devices," IEEE J. Emerg. Sel. Topics Circuits Syst., vol. 9, no. 2, pp. 292–308, Jun. 2019.

- [3] K. Bhardwaj and S. M. Nowick, "A continuous-time replication strategy for efficient multicast in asynchronous NoCs," IEEE Trans. Very Large Scale Integration. (VLSI) System, vol. 27, no. 2, pp. 350–363, Feb. 2019.

- [4] M. F. Reza and P. Ampadu, "Energy-efficient and high-performance NoC architecture and mapping solution for deep neural networks," in Proc. 13th IEEE/ACM Int. Symp. Netw.-Chip, Oct. 2019, pp. 1–8.

- [5] X. Zhou et al., "Cambricon-S: Addressing irregularity in sparse neural networks through a cooperative software/hardware approach," in Proc. 51st Annu. IEEE/ACM Int. Symp. Micro architecture (MICRO), Oct. 2018, pp. 15–28

- [6] Kwon, A. Samajdar, and T. Krishna, "MAERI: Enabling flexible dataflow mapping over DNN accelerators via reconfigurable interconnects," in Proc. 23rd Int. Conf. Archit. Support Program. Lang. Oper. Syst. (ASPLOS), Mar. 2018, pp. 461–475.

- [7] A. Firuzan, M. Modarressi, M. Daneshtalab, and M. Reshadi, "Reconfigurable network-on-chip for 3D neural network accelerators," in Proc. 12th IEEE/ACM Int. Symp. Netw.-Chip (NOCS), Oct. 2018, pp. 1–8.

- [8] B. Bohnenstiehl et al., "KiloCore: A 32-nm 1000-processor computational array," IEEE J. Solid-State Circuits, vol. 52, no. 4, pp. 891–902, Apr. 2017.

- [9] K. He, X. Zhang, S. Ren, and J. Sun, "Identity mappings in deep residual networks," in Proc. Eur. Conf. Compute. Vis. (ECCV), Oct. 2016, pp. 630–645.

- [10] C. Zhang, P. Li, G. Sun, Y. Guan, B. Xiao, and J. Cong, "Optimizing FPGA-based accelerator design for deep convolution neural networks," in Proc. ACM/SIGDA Int. Symp. Field-Program. Gate Arrays (FPGA), Feb. 2015, pp. 161–170

- [11] S. Gupta, A. Agrawal, K. Gopalakrishnan, and P. Narayanan, "Deep learning with limited numerical precision," in Proc. Int. Conf. Mach. Learn. (ICML), Jul. 2015, pp. 1737–1746.

- [12] A. Touzene, "On all-to-all broadcast in dense Gaussian network onchip," IEEE Trans. Parallel Distrib. Syst., vol. 26, no. 4, pp. 1085–1095, Apr. 2015.

- [13] R. Girshick, J. Donahue, T. Darrell, and J. Malik, "Rich feature hierarchies for accurate object detection and semantic segmentation," in Proc. IEEE Conf. Comput. Vis. Pattern Recognit., Jun. 2014, pp. 580–587.

- [14] P. Ou et al., "A 65 nm 39 GOPS/W 24-core processor with 11Tb/s/W packet-controlled circuit-switched double-layer network-on-chip and heterogeneous execution array," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2013, pp. 56–57.

- [15] G. Hinton et al., "Deep neural networks for acoustic modeling in speech recognition: The shared views of four research groups," IEEE Signal Process. Mag., vol. 29, no. 6, pp. 82–97, Nov. 2012.